Nibbler 4-bit CPU in VHDL Raw NibblerCPUvhd This file contains bidirectional Unicode text that may be interpreted or compiled differently than what appears below. 4 BIT MICROPROCESSOR DESIGN USING VHDL In partial fulfilment of the requirement for the award of the degree of Bachelor of Technology in.

Vhdl Code For Arithmetic Logic Unit Alu Fpga4student Com

Include addition subtraction and shifting We proposed arithmetic and logic unit using VHDL structural and dataflow level design.

. The statement are used for iterating a well-defined task. Today the VHDL code for the MIPS Processor will be presented. Mohd Kashif Create Date.

Out signed3 downto 0. A simple VHDL testbench for the MIPS processor will be also provided for simulation purposes. Here the microprocessor is divided into various sub modules and each of them was programmed using VHDL.

As the logic is time critical and the AVR too slow to handle it I decided to implement it in a Xilinx Spartan FPGA. This paper involves the design and simulation of 16 bit microprocessor architecture on FPGA using VHDL. Hello everyone I am new to VHDL and I have to write behavioral vhdl code for a 4-bit register with parallel load using a D-Flip Flop.

Rupali Jarwal Ulka Khire 4-Bit Arithmetic And Logic Unit Design Using Modelling In VHDL International Journal of Engineering Research Technology IJERT Vol. In signed3 downto 0. The design is a memory decoder common in microprocessor systems.

131230 07012013 Design Name. Information Technology Submitted by. Designing of 8-bit microprocessor using VHDL.

VHDL Code for 4-bit ALU library IEEE. Component of a microprocessor and is the core This paper presents design concept of 4-bit arithmetic and logic unit ALU. Format Unconditional JMP instruction.

Scope of the Project Design an 8 bit microprocessor using VHDL. 4 BIT ALU using VHDL In this blog post we will be learning about logical and arithmetic operators using a system design approach in VHDL. 4-bit ALU Module Name.

In STD_LOGIC_VECTOR 2 downto 0. Design methodology has been changing from schematic design to HDL based design. However its creators were pin-limited the 4004 DIL package had only 16 pins so the data and address were multiplexed on the same four wires with the address being written out in three 4-bit chunks.

This paper describes the realization of a 4-bit FPGA based simple low cost processor implemented on the Xilinx Spartan 3 xc3s200FT256 using. These flags are used to decide whether the condition to be checked for each of these jumps is true or not. A Design the PREP benchmark 9 shown in Fig.

As stated before the compare instruction also sets the flags of the processor. Where earlier a design may have included 6 to 10 ASICs. How to concatenate 3 operation select bits in a 4-bit ALU design - VHDL.

Conditional Jumps JZ and JNZ. Opcode4-bits Unused 4-bits 8-bit offset Immediate Fig. Loop statements are a catagory of control structures that allow you to specify repeating sequences of behavior in a circuit.

2 Issue 3 March - 2013 4-Bit Arithmetic And Logic Unit Design Using Structural Modelling In VHDL Rupali Jarwal1 and Ulka Khire2 1 2 Microelectronics and VLSI Design Electronics Instrumentation Engineering department SGSITS Indore MP India Abstract Arithmetic Logic Unit ALU is a. A Project Report on. LaMeresThe microcontroller has an 8-bit processor a 128-byte program memory a 96-byte RAM 16x8-bit output ports and 16x8-bit input ports.

The preliminary goal will be to have a microprocessor capable of executing simple mathematical operations. To review open the file in an editor that reveals hidden Unicode characters. International Journal of Engineering Research Technology IJERT ISSN.

The design is a memory decoder common in microprocessor systems. VHDL has following types of iterative statements. In each iteration it then increaments or decrement some local identifier for use inside the LOOP statement.

Entity alu is Port inp_a. In signed3 downto 0. The design would then be implemented by putting it on an FPGA.

Here is the D-FF code i have to use. Significant features such as the increased speed minimal implementation real-estate reduction in power and maximum configurability are provided by several FPGAs. The instruction set and architecture of the 8-bit microcontroller are available at Chapter 13 in the book Introduction to Logic Circuits and Logic Design with VHDL by prof.

With 5 gates for a 41 multiplexer and an 8 bit wide data path. ALU Behavioral Project Name. VHDL Prentice Hall 2000 8 Jikku Jeemon pipelined 8- bit RISC processor design using Verilog HDL on FPGA IEEE international conference in electronics information communication Technology pp.

The project is a 4-bit ALU in VHDL with a total of 16 operations which includes various arithmetic logical and data calculations performed by coding the ALU in VHDL code. 2 Digital logic and microprocessor design using VHDL By Hwang 3 Design and Implementation of a 8 bit RISC Processor on Xilinx FPGA Wael M ElMedany Khalid A AlKoohej Engineering faculty of Engineering Fayoum University Egypt. So I have this lab assignment which carries on from a previous one where I implemented a single bit ALU in VHDL.

The structural VHDL model of the microprocessor is designed to perform 16 operations which include both logical and arithmetic operation. Implementing a CPU in VHDL Part 1. Scope of the project.

Architecture Behavioral of alu is begin processinp_a inp_b sel begin case sel is when 000. An Arithmetic and Logic Uni t is a digital circuit which performs arithmetic logical and shift operations. Kajari Sur Department of Information Technology Academic Year 2011-2015.

Help in vhdl Dear friends I am making a 4-bit microprocessor using VHDL. I shall be highly thankful to you. The single bit ALU module takes an opcode and performs an operation based on this op.

For a recent private project I had to extend a design based on an AVR controller with a fair amount of custom logic. Department ComputerEngineering Information Technology College University Of Bahrain 32038 Bahrain 4 V. This paper presents the VHDL implementation of a 32-bit microprocessor.

Last time I presented a Verilog code for a 16-bit single-cycle MIPS processorThe instruction set and architecture design for the MIPS processor was provided here. 2023 -2027 9 Tessy Ninan Design and Anlysis of bit microprocessor using xilinx tool IEEE international journal scientific research engineering. Sanjona Mazumder Registration No.

Entity dff is port d. 111040110160 Roll No10400211064 Prof. 2 Issue 3 March.

As an aside the worlds first commercial microprocessor the Intel 4004 also had a 4-bit data bus and a 12-bit address bus. The addresses are decoded only.

Design A Simple Microprocessor In Vhdl

Building A 4 Bit Computer From The Ground Up

Building A 4 Bit Computer From The Ground Up

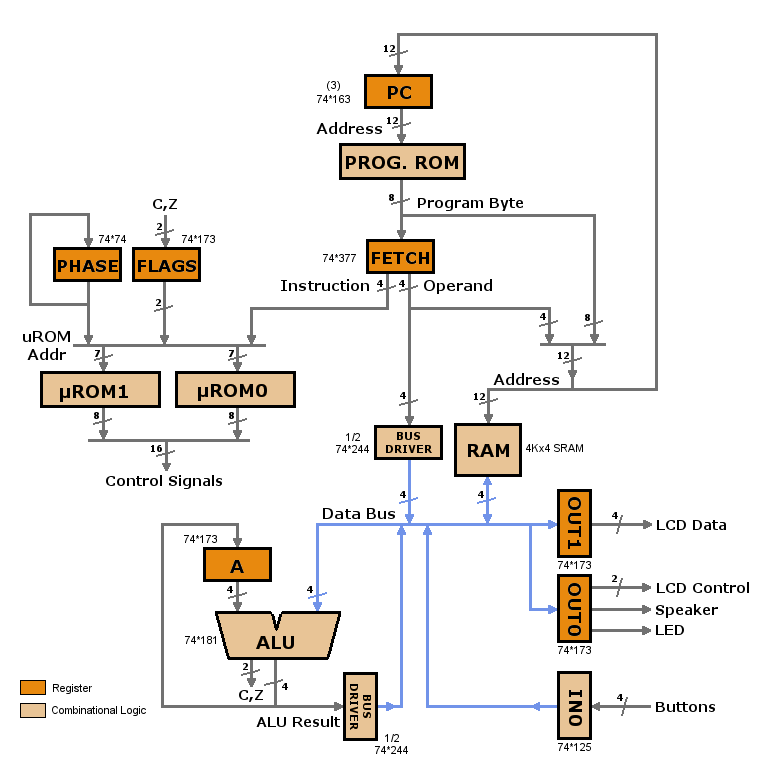

Nibbler 4 Bit Cpu Big Mess O Wires

4 Bit Microprocessor Design Using Vhdl Pdf Central Processing Unit Microprocessor

Building A 4 Bit Computer From The Ground Up

Pdf 4 Bit Processing Unit Design Usingvhdl Structural Modeling For Multiprocessor Architecture

Minimalist 4 Bit Processor Focused On Processors Theory Teaching Semantic Scholar

0 comments

Post a Comment